Desde la perspectiva de un entusiasta de la informática x86 tradicional (o profesional), los mainframes son bestias arcaicas y extrañas. Son físicamente enormes, consumen mucha energía y son costosos en comparación con los equipos de centros de datos más tradicionales, y generalmente ofrecen menos computación por rack a un costo más alto.

Esto plantea la pregunta: “¿Por qué seguir usando mainframes, entonces?” Una vez que agita con la mano las respuestas cínicas que se reducen a “porque así es como siempre lo hemos hecho”, las respuestas prácticas se reducen en gran medida a la fiabilidad y la coherencia. Como señala Ian Cutress de AnandTech en un especulativo pieza centrado en el caché rediseñado de Telum, “el tiempo de inactividad de estos [IBM Z] sistemas se mide en milisegundos por año “. (Si es cierto, eso es al menos Siete nueves.)

Propio de IBM anuncio de Telum insinúa cuán diferentes son las prioridades de la computación básica y de mainframe. Describe casualmente la interfaz de memoria de Telum como “capaz de tolerar un canal completo o fallas DIMM, y diseñada para recuperar datos de manera transparente sin afectar el tiempo de respuesta”.

Cuando extrae un DIMM de un servidor x86 activo y en ejecución, ese servidor no “recupera datos de forma transparente”, simplemente falla.

Arquitectura de la serie Z de IBM

Telum está diseñado para ser una especie de chip único para gobernarlos a todos para mainframes, reemplazando una configuración mucho más heterogénea en mainframes IBM anteriores.

La CPU IBM z15 de 14 nm que Telum está reemplazando cuenta con cinco procesadores en total: dos pares de procesadores de cómputo de 12 núcleos y un controlador de sistema. Cada procesador de cómputo aloja 256MiB de caché L3 compartido entre sus 12 núcleos, mientras que el controlador del sistema alberga la friolera de 960MiB de caché L4 compartido entre los cuatro procesadores de cómputo.

Cinco de estos procesadores z15, cada uno de los cuales consta de cuatro procesadores de cómputo y un controlador de sistema, constituyen un “cajón”. Cuatro cajones se unen en un solo mainframe alimentado por z15.

Aunque el concepto de múltiples procesadores en un cajón y múltiples cajones en un sistema permanece, la arquitectura dentro de Telum es radicalmente diferente y considerablemente simplificada.

Arquitectura de armas

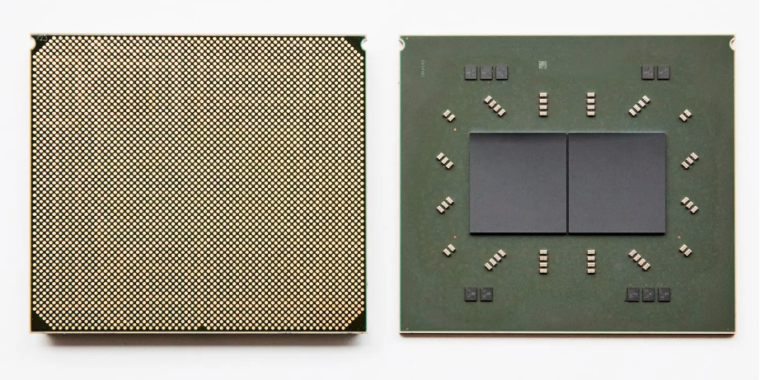

Telum es algo más simple a primera vista que z15: es un procesador de ocho núcleos construido sobre el proceso de 7 nm de Samsung, con dos procesadores combinados en cada paquete (similar al enfoque chiplet de AMD para Ryzen). No hay un procesador de controlador de sistema separado; todos los procesadores de Telum son idénticos.

A partir de aquí, cuatro paquetes de CPU Telum se combinan para hacer un “cajón” de cuatro sockets, y cuatro de esos cajones entran en un solo sistema de mainframe. Esto proporciona 256 núcleos en total en 32 CPU. Cada núcleo se ejecuta en un base frecuencia de reloj superior a 5 GHz, lo que proporciona una latencia más predecible y consistente para transacciones en tiempo real que una base más baja con una tasa de turbo más alta.

Bolsillos llenos de caché

Eliminar el procesador del sistema central en cada paquete significó rediseñar también la caché de Telum: la enorme caché de 960MiB L4 se ha ido, así como la caché L3 compartida por dado. En Telum, cada núcleo individual tiene una caché L2 privada de 32MiB, y eso es todo. No hay caché de hardware L3 o L4 en absoluto.

Aquí es donde las cosas se ponen profundamente extrañas, mientras que la caché de 32MiB L2 de cada núcleo Telum es técnicamente privada, en realidad es solo virtualmente privado. Cuando se expulsa una línea de la caché L2 de un núcleo, el procesador busca un espacio vacío en la L2 de los otros núcleos. Si encuentra alguno, la línea de caché L2 desalojada del núcleo X se etiqueta como una línea de caché L3 y se almacena en el núcleo yde L2.

Bien, tenemos un caché L3 virtual compartido de hasta 256MiB en cada procesador Telum, compuesto por el caché L2 “privado” de 32MiB en cada uno de sus ocho núcleos. A partir de aquí, las cosas van un paso más allá: los 256MiB de “L3 virtual” compartida en cada procesador pueden, a su vez, usarse como “L4 virtual” compartida entre todos los procesadores de un sistema.

La “L4 virtual” de Telum funciona en gran medida de la misma manera que su “L3 virtual” en primer lugar: las líneas de caché L3 expulsadas de un procesador buscan un hogar en un procesador diferente. Si otro procesador en el mismo sistema Telum tiene espacio libre, la línea de caché L3 desalojada se vuelve a etiquetar como L4 y vive en la L3 virtual en el otro procesador (que se compone de las L2 “privadas” de sus ocho núcleos).

Ian Cutress de AnandTech entra en más detalle en los mecanismos de caché de Telum. Finalmente, los resume respondiendo “¿Cómo es esto posible?” con una simple “magia”.

Aceleración de inferencia de IA

Christian Jacobi de IBM describe brevemente la aceleración de la IA de Telum en este clip de dos minutos.

Telum también presenta un acelerador de inferencia en matriz 6TFLOPS. Está diseñado para utilizarse, entre otras cosas, para la detección de fraudes en tiempo real. durante transacciones financieras (a diferencia de poco después de la transacción).

En la búsqueda de un rendimiento máximo y una latencia mínima, IBM enhebra varias agujas. El nuevo acelerador de inferencia se coloca en la matriz, lo que permite interconexiones de latencia más baja entre el acelerador y los núcleos de la CPU, pero es no integrado en los propios núcleos, al estilo del conjunto de instrucciones AVX-512 de Intel.

El problema con la aceleración de inferencia en el núcleo como la de Intel es que normalmente limita la potencia de procesamiento de IA disponible para cualquier núcleo. Un núcleo Xeon que ejecuta una instrucción AVX-512 solo tiene el hardware dentro de su propio núcleo disponible, lo que significa que los trabajos de inferencia más grandes deben dividirse entre varios núcleos Xeon para extraer el rendimiento completo disponible.

El acelerador de Telum está en marcha pero fuera de núcleo. Esto permite que un solo núcleo ejecute cargas de trabajo de inferencia con el poder del completo acelerador en la matriz, no solo la parte incorporada en sí mismo.

Listado de imagen por IBM